Prepared by: Ding Hongfei

### Introduction

The chip communication protocol is now provided. This manual has marked the meanings of the internal registers of the chip, which facilitates customers to directly refer to them.

## 1. Programming guide

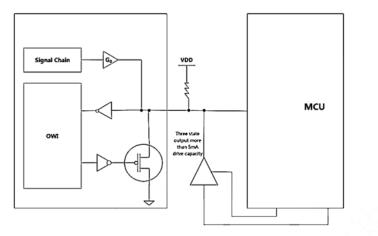

Figure 1 Schematic diagram of the OWI hardware interface

Power on and enter the window period of OWI (One-Wire Interface)

The GSA301 provides current-limiting output to the Vout pin for the first 20/100ms window after the end of the internal POR (Power On Reset) and allows the OWI programming interface to be activated by external circuits (this window can be programmed to close permanently, It is recommended that customers choose whether to turn off according to their own application environment).GSA301 needs power supply coordination to enter the communication. \*Note1: In this process, it is recommended that the customer use a three-state output gate with an output capacity of more than 5mA to force the Vout signal to the digital level of '0' or '1' to enable the OWI interface of the GSA301 to be activated.

■ Temporary exit of OWI communication

During the module level calibration of the current sensor, the customer can write any value to the 0x20 register to temporarily exit the OWI interface communication and restore the Go current-limiting output (current limiting to 1mA). After a waiting period(the length of which is determined by the values of the two registers 0x21 and 0x22), the GSA301 will automatically re-enter the OWI communication mode and turn off the Go output.

■ Permanent shutdown of OWI communication

In most application scenarios, the customer does not want the chip to enter the OWI mode after the factory calibration and burning NVM. If there is such a need, the customer can burn the NVM address 0x30 register value bit0 set to 1, so that after the next power-on there will be no more 20/100ms OWI window period, OWI programming interface is permanently closed. After the OWI communication is permanently turned off, the GSA301 directly outputs the analog semaphore normally 1ms after powering on the POR.

MS-AN-24006

Data: 2024.12.16

# MS-AN-24006

## 2. Register Description

Debugging and calibration register area

The debugging and calibration register area of GSA301 is mainly used for customers to do system calibration, debugging and control when burning NVM. The data in the debug and calibration register area will not be saved after power failure. The address space of the register area is from 0x00 to 0x12.

|           | Table 1 Deta | ils of GSA301 deb | bug and calibrate register area address                                                                                                                      |         |           |      |

|-----------|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|------|

| Address   | write        |                   | Features                                                                                                                                                     | Default | 0x0A      | RW   |

| 0x00      |              |                   | Write 0x24 to this register, software reset chip                                                                                                             | 0x00    | UXUA      | IX W |

| 0x01~0x05 | NA           | NA                | NA                                                                                                                                                           | NA      |           |      |

| 0x06      | R            | TADC_H            | 12-bit TADC current conversion value<br>data 4 bits higher (Bit7~4 are all zeros)                                                                            | 0x00    |           |      |

| 0x08      | RW           | ZeroDAC_H         | 14 bit zero bias fine-tune register high<br>6 bits with calibration mode not<br>enabled, read only, the value is the<br>value of the current ZeroDAC control |         | 0x0B      | RW   |

|           |              |                   | immediately changes the ZeroDAC                                                                                                                              |         | 0x0C~0x0F | NA   |

|           |              |                   | control word and acts as an output.                                                                                                                          |         | 0x10      | RW   |

| inly used for customers to do<br>ata in the debug and calibration<br>f the register area is from 0x00          |                        | 0x09      | RW | ZeroDAC_L  | 14 bit zero bias fine tune register 8 bits<br>lower<br>Calibration mode not enabled, read<br>only, value is the value of the control<br>word of the current ZeroDAC<br>When calibrating mode is enabled (see<br>Register 0x10), writing this register | 0x00 |

|----------------------------------------------------------------------------------------------------------------|------------------------|-----------|----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                |                        |           |    |            | immediately changes the ZeroDAC control word and acts as an output.                                                                                                                                                                                   |      |

| area address                                                                                                   |                        |           |    |            | 14 bit gain fine-tuned register High 6<br>bits When calibrating mode is not<br>enabled, read only, the value is the                                                                                                                                   |      |

| es<br>ster, software                                                                                           | <b>Default</b><br>0x00 | 0x0A      | RW | GainDAC_H  | value of the current GainDAC control<br>word When calibrating mode is enabled<br>(see register 0x10), writing this register                                                                                                                           | 0x00 |

| · 1                                                                                                            | NA                     |           |    |            | immediately changes the GainDAC control word and acts as an output.                                                                                                                                                                                   |      |

| onversion value<br>7~4 are all zeros)                                                                          | 0x00                   |           |    |            | 14 bit gain fine-tuned register Low 8                                                                                                                                                                                                                 |      |

| ne register high<br>mode not<br>value is the<br>croDAC control<br>0x00<br>e is enabled (see<br>g this register |                        | 0x0B      | RW | GainDAC_L  | bits When calibrating mode is not<br>enabled, read only, the value is the<br>value of the current GainDAC control<br>word When calibrating mode is enabled                                                                                            | 0x00 |

|                                                                                                                |                        |           |    |            | (see register 0x10), writing this register<br>immediately changes the GainDAC<br>control word and is used for output.                                                                                                                                 |      |

| he ZeroDAC                                                                                                     |                        | 0x0C~0x0F | NA | NA         | NA                                                                                                                                                                                                                                                    | NA   |

| as an output.                                                                                                  |                        | 0x10      | RW | Calib_Mode | Bit0: Calibration mode enabled                                                                                                                                                                                                                        | 0x00 |

|      |    |            | • Set 0- Without using calibration   |      |

|------|----|------------|--------------------------------------|------|

|      |    |            | mode, the value of register 0x08 to  |      |

|      |    |            | 0B is the GainDAC and ZeroDAC        |      |

|      |    |            | values written to the response       |      |

|      |    |            | register after calibration.          |      |

|      |    |            | • Set 1- activates calibration mode, |      |

|      |    |            | allowing registers 0x08~0B to be     |      |

|      |    |            | written.                             |      |

|      |    |            | Bit1:Blow_Start                      |      |

|      |    |            | • Set 1- start burn write NVM        |      |

|      |    |            | (customers need to wait in the       |      |

| 0x12 | RW | Blow_Start | software for some time before        | 0x00 |

|      |    |            | doing other read and write           |      |

|      |    |            | operations).                         |      |

|      |    |            |                                      |      |

■ NVM Global Control Variable area

The global control variable area of GSA301 is primarily used to control options that are not relevant for customer and system calibration. In general, this area saves the settings without the need for secondary programming.

| Table 2 Details of GSA301 NVM       | global control variable area address |

|-------------------------------------|--------------------------------------|

| Table 2 Details of OSASOT IN VIVI S | giobal control variable alea address |

| Address | Read and<br>write | Name       | Features                                                                                                                                     | Comments |

|---------|-------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0x30    | RW<br>Blow        | Sys_Config | <ul> <li>Bit7: MTP_EN<br/>set 0: NVM customer<br/>calibration parameter area<br/>using OTP mode (when<br/>OTP mode is used, Bank1</li> </ul> |          |

|   | data and corresponding        |

|---|-------------------------------|

|   | Bank2 data are done or        |

|   | logical as the actual         |

|   | configuration value).         |

|   | set 1: NVM customer           |

|   | calibration parameter area    |

|   | uses MTP mode (When           |

|   | using MTP mode, customer      |

|   | uses Bit6 of register 0x30 to |

|   | select Bank1 data or a set of |

|   | Bank2 data as the actual      |

|   | configuration value).         |

|   | Only when set to MTP          |

|   | mode can you burn 3 times.    |

| • | Bit6:CONFIG_MTP_SEL           |

|   | (works only in MTP mode)      |

|   | set 0: ConfigBank1 data,      |

|   | Bank1 points to register      |

|   | 0x40/0x41                     |

|   | set 1: ConfigBank2 data,      |

|   | Bank2 points to register      |

|   | 0x42/0x43                     |

| • | Bit5: Set to 1                |

| • | Bit4~1:                       |

|   | One programming:              |

|   | LUT_TABLE_BANK_SEL            |

|   | <3:0> 0001b: use the data in  |

|   | LUTBank1 as the power-on      |

|   | default values for GainDAC    |

|   | and ZeroDAC, as well as the   |

|              |          | <ul> <li>block for fixed output.</li> <li>Secondary programming:</li> <li>LUT_TABLE_BANK_SEL</li> <li>&lt;3:0&gt; 0011b: use the data in</li> <li>LUTBank3 as the power-on</li> <li>default values for GainDAC</li> <li>and ZeroDAC, as well as the</li> <li>block for fixed output.</li> <li>Tertiary programming:</li> <li>LUT_TABLE_BANK_SEL</li> <li>&lt;3:0&gt; 0111b: use the data in</li> <li>LUTBank7 as the power-on</li> <li>default values for GainDAC</li> <li>and ZeroDAC, as well as the</li> <li>block for fixed output.</li> <li>Bit0: OWI_Disable</li> <li>set 0: The OWI interface is</li> <li>not disabled.</li> <li>set 1: The OWI interface is</li> <li>permanently disabled, and</li> <li>there is no 20/100ms</li> <li>window after it is started</li> </ul> | 0x32<br>0x33 | RW<br>Blow<br>RW<br>Blow | CSTCTrim1<br>CSTCTrim1 | <ul> <li>(5V power supply,<br/>operating temperature is<br/>higher than 105°C for use)<br/>0011b: current drive 3mA</li> <li>(5V power supply,<br/>operating temperature is<br/>lower than 105°C for use)</li> <li>Bit3: VEXC_SEL<br/>set 1: 2.5V (3.3V power<br/>supply)</li> <li>Bit2: INPUT_SWAP<br/>set 0: the input positive and<br/>negative are not exchanged.</li> <li>Bit1~0: SPIN_CHIP<br/>10b : enables the<br/>self-stabilized zero<br/>function.</li> <li>Bit6~0: IEXC_TC1&lt;6:0&gt;</li> </ul> | TC1 values<br>between 0 and<br>63 |

|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 0x31 R<br>Bl | sys_comg | <ul> <li>Bit7~4: EXC Config<br/>0000b: current drive 1.5mA<br/>(used on 3.3V power<br/>supply)<br/>0010b: current drive 2.5mA</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |

# Matrixsens

■ NVM customer calibration parameter area

The NVM customer calibration parameter area of GSA301 is divided into Block1 and Block2 data pieces.

1) In OTP mode, the two pieces of data backup each other, and the final output value is the calculation result of the corresponding data "or" of Block1 and Block2.

2) In MTP mode, the customer can choose one of the data of Block1 or Block2 as the final

output result. The data for Block1 starts from address 0x40 to 0x41, and the data for Block2

starts from addresses 0x42 to 0x43.

| Address | Read and<br>write | Name         | Feature                                                                                                                                                                                                                                                     | Comments |

|---------|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0x40    | RW<br>Blow        | GAIN Setting | <ul> <li>Bit7~6: Go gain configuration<br/>00b: 2.4x<br/>01b: 2.8x<br/>10b: 3.2x<br/>11b: 3.6x</li> <li>Bit5~3: G2 gain configuration<br/>000b: 1.182x<br/>001b: 1.4x<br/>010b: 1.667x<br/>011b: 2x<br/>100b: 2.429x<br/>101b: 3x<br/>110b: 3.5x</li> </ul> | MTPBank1 |

Table 3 Detailed description of GSA301 NVM customer calibration parameter area address

|      |      |              | 111b: 4x                        |          |

|------|------|--------------|---------------------------------|----------|

|      |      |              | • Bit2~0: G1 gain configuration |          |

|      |      |              | 000b:1x                         |          |

|      |      |              | 001b:2x                         |          |

|      |      |              | 010b:4x                         |          |

|      |      |              | 011b:8x                         |          |

|      |      |              | 100b:16x                        |          |

|      |      |              | 101b:32x                        |          |

|      |      |              | 110b:64x                        |          |

|      |      |              | 111b:128x                       |          |

|      |      |              | • Bit0: output mode             |          |

|      |      |              | set 0: fixed output, gain does  |          |

|      |      |              | not change with                 |          |

|      |      |              | power supply                    |          |

|      |      |              | set 1: proportional output,     |          |

|      |      |              | gain changes with               |          |

|      |      |              | power supply                    |          |

|      |      |              | • Bit2~1: Vbias/V0 control      |          |

|      | DW   | EXC          | 00b: Vbias output is 2.5V       |          |

| 0x41 | RW   | Config&      | 01b: Vbias output is 1.65V      | MTPBank1 |

|      | Blow | Input Option | 10b: Vbias output is 0.5V       |          |

|      |      |              | When set to                     |          |

|      |      |              | 00b/01b/10b, both               |          |

|      |      |              | zero and reference              |          |

|      |      |              | voltage are fixed               |          |

|      |      |              | outputs.                        |          |

|      |      |              | 11b:Vbias/V0 output             |          |

|      |      |              | 1/2VCC When set to              |          |

|      |      |              | 11b both zero and               |          |

|      |      |              | reference voltage are                       |          |      |            |                                | 101b:32x                                     |           |

|------|------|--------------|---------------------------------------------|----------|------|------------|--------------------------------|----------------------------------------------|-----------|

|      |      |              | proportional outputs.                       |          |      |            |                                | 110b:64x                                     |           |

|      |      |              | <ul> <li>Bit3~4: Low pass filter</li> </ul> |          |      |            |                                | 111b:128x                                    |           |

|      |      |              | frequency selection                         |          |      |            |                                | • Bit0: output mode                          |           |

|      |      |              | 00b: Not recommended                        |          |      |            |                                | set 0: fixed output, gain does               |           |

|      |      |              | 01b: 500kHz                                 |          |      |            |                                | not change with                              |           |

|      |      |              | 10b: 250kHz                                 |          |      |            |                                | power supply                                 |           |

|      |      |              | 11b: 50kHz                                  |          |      |            |                                | set 1: proportional output,                  |           |

|      |      |              | ● Bit7~5: NA                                |          |      |            |                                | gain changes with                            |           |

|      |      |              | • Bit7~6: Go gain configuration             |          |      |            |                                | power supply                                 |           |

|      |      |              | 00b: 2.4x                                   |          |      |            | EXC<br>Config&<br>Input Option | <ul> <li>Bit2~1: Vbias/V0 control</li> </ul> |           |

|      |      | GAIN Setting | 01b: 2.8x                                   |          |      |            |                                | 00b: Vbias output is 2.5V                    | MTP Bank2 |

|      |      |              | 10b: 3.2x                                   |          |      |            |                                | 01b: Vbias output is 1.65V                   |           |

|      |      |              | 11b: 3.6x                                   |          |      |            |                                | 10b: Vbias output is 0.5V                    |           |

|      |      |              | • Bit5~3: G2 gain configuration             |          |      |            |                                | When set to                                  |           |

|      |      |              | 000b: 1.182x                                |          | 0.42 | RW<br>Blow |                                | 00b/01b/10b, both                            |           |

|      |      |              | 001b: 1.4x                                  |          | 0x43 |            |                                | zero and reference                           |           |

|      |      |              | 010b: 1.667x                                |          |      |            |                                | voltage are fixed                            |           |

| 0.40 | RW   |              | 011b: 2x                                    |          |      |            |                                | outputs.                                     |           |

| 0x42 | Blow |              | 100b: 2.429x                                | MTPBank2 |      |            |                                | 11b:Vbias/V0 output                          |           |

|      |      |              | 101b: 3x                                    |          |      |            |                                | 1/2VCC When set to                           |           |

|      |      |              | 110b: 3.5x                                  |          |      |            |                                | 11b both zero and                            |           |

|      |      |              | 111b: 4x                                    |          |      |            |                                | reference voltage are                        |           |

|      |      |              | • Bit2~0: G1 gain configuration             |          |      |            |                                | proportional outputs.                        |           |

|      |      |              | 000b:1x                                     |          |      |            |                                | • Bit3~4: Low pass filter                    |           |

|      |      |              | 001b:2x                                     |          |      |            |                                | frequency selection                          |           |

|      |      |              | 010b:4x                                     |          |      |            |                                | 00b: Not recommended                         |           |

|      |      |              | 011b:8x                                     |          |      |            |                                | 01b: 500kHz                                  |           |

|      |      |              | 100b:16x                                    |          |      |            |                                | 10b: 250kHz                                  |           |

# Matrixsens

|                   |                      |                                                                                                                          | 11b: 50kHz<br>● Bit7~5: NA                                                                                                                                                                                                           |                                                 |

|-------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

|                   |                      | Table 4 GSA                                                                                                              | 01 3 times programming data storage location                                                                                                                                                                                         |                                                 |

| Address           | Read<br>and<br>write | Name                                                                                                                     | Feature                                                                                                                                                                                                                              | Comments                                        |

| 0x60<br>~<br>0x64 | RW<br>Blow           | Room<br>temperatu<br>point:<br>12bit<br>temperatu<br>value, 14l<br>ZeroDA<br>control wo<br>14bit<br>GainDA<br>control wo | $\begin{tabular}{ c c c c c } \hline TADC(3:0) & \hline TADC(3:10) \\ \hline TADC(3:0) & \hline ZeroDAC(9:2) \\ \hline \hline ZeroDAC(1:0) & \hline GainDAC(13:8) \\ \hline \hline I, & \hline GainDAC(7:0) \\ \hline \end{tabular}$ | One<br>programming<br>write: LUT -<br>BANK1     |

| 0x70<br>~<br>0x74 | RW<br>Blow           | Room<br>temperatu<br>point:<br>12bit<br>temperatu<br>value, 14l<br>ZeroDA0<br>control wo<br>14bit<br>GainDA0             | TADC<11:4>         TADC<3:0>       ZeroDAC<13:10>         ZeroDAC<9:2>       ZeroDAC<13:8>         ZeroDAC<1:0>       GainDAC<13:8>                                                                                                  | Secondary<br>programming<br>write: LUT<br>BANK3 |

|      |           | Room<br>temperature<br>point: |              |                               | _                     |

|------|-----------|-------------------------------|--------------|-------------------------------|-----------------------|

|      |           | 12bit                         | TA           | DC<11:4>                      | Tertiary              |

| 0x85 | RW        | temperature                   | TADC<3:0>    | $ZeroDAC\langle 13:10\rangle$ | - programming:        |

| ~    | Blow      | value, 14bit                  | Zer          | ZeroDAC(9:2)                  |                       |

| 0x89 | DIOW      | ZeroDAC                       | ZeroDAC<1:0> | GainDAC<13:8>                 | - write: LUT<br>BANK7 |

|      |           | control word,                 | Gai          | nDAC<7:0>                     | DAINK/                |

|      |           | 14bit                         |              |                               |                       |

|      | $\sim$    | GainDAC                       |              |                               |                       |

|      | $\sim 17$ | control word                  |              |                               |                       |

#### Chip read/write timing instructions

a)Read: Enter the calibration mode after communication, issue the read command, and after

about 1ms, the chip Vout foot will output the signal corresponding to the read command;

b)Write: After writing the register value, assign any value to the register 0x20, the chip can

briefly exit the communication, and the Vout foot has a stable output voltage after about 0.1s.

## Important Notice and Disclaimer

The product application information and other similar content described in this document may be replaced by updated content. Matrixsens makes no representations or warranties, express or implied, written or oral, statutory or otherwise, regarding such information, including but not limited to representations or warranties regarding its usage, quality, performance, merchantability or fitness for a particular purpose.

This application manual is available for professional technicians to use Matrixsens products for model selection and application. You will assume sole and full responsibility for the following actions: (1) selecting appropriate Matrixsens products for your application; (2) designing, validating and testing your application; (3) ensuring that your application meets the corresponding standards as well as any other safety, security or other requirements. Any changes to this application manual will be made without prior notice. Matrixsens' authorization for your use of this application manual is limited to the relevant applications of Matrixsens products involved in the development resources. Except for this, this application manual shall not be copied or displayed, and no authorization license for the intellectual property rights of other Matrixsens or any third parties will be provided. Matrixsens shall not be responsible for any claims, compensations, costs, losses and liabilities arising from the use of this application manual, and you must compensate for the losses caused thereby to Matrixsens and its representatives.